Chapter 7

- Mampu Membuat Rangkaian Full substractor, half substractor dan Four-bit subtractor.

- Memahami Fungsi Komponen pada Full substractor, half substractor dan Four-bit subtractor.

- Mengetahui Prinsip Kerja dari Rangkaian Full substractor, half substractor dan Four-bit subtractor.

- Gerbang AND

- Gerbang OR

- Gerbang XOR

- Gerbang NOT

- Logic State

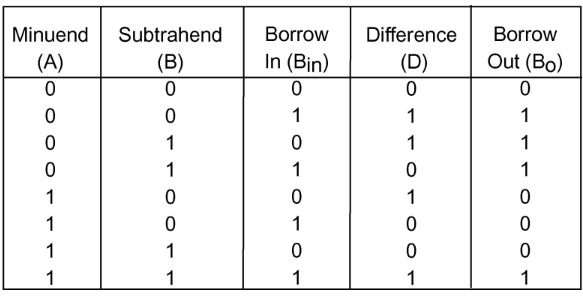

1) 7.14 Rangkaian Full Substractor

Full Subtractor adalah sirkuit logika kombinasional dalam elektronika digital yang dirancang untuk melakukan operasi pengurangan pada tiga buah bit biner pada satu waktu. Ini berbeda dengan Half Subtractor yang hanya mengurangi dua bit. Full Subtractor sangat penting untuk melakukan pengurangan biner multi-bit, karena dapat menangani bit "pinjaman" (borrow) dari posisi bit sebelumnya.

Tujuan utama Full Subtractor adalah menghitung selisih (difference) antara dua bit masukan, sambil memperhitungkan kemungkinan adanya "pinjaman" (borrow) yang masuk dari posisi bit yang lebih rendah.

Fungsinya dapat dianalogikan dengan cara kita melakukan pengurangan desimal bersusun, di mana kita terkadang perlu "meminjam" dari kolom di sebelah kiri. Dalam biner, ini disebut "Borrow In" (masukan pinjaman) dan "Borrow Out" (keluaran pinjaman).

Full Subtractor memiliki tiga masukan dan dua keluaran:

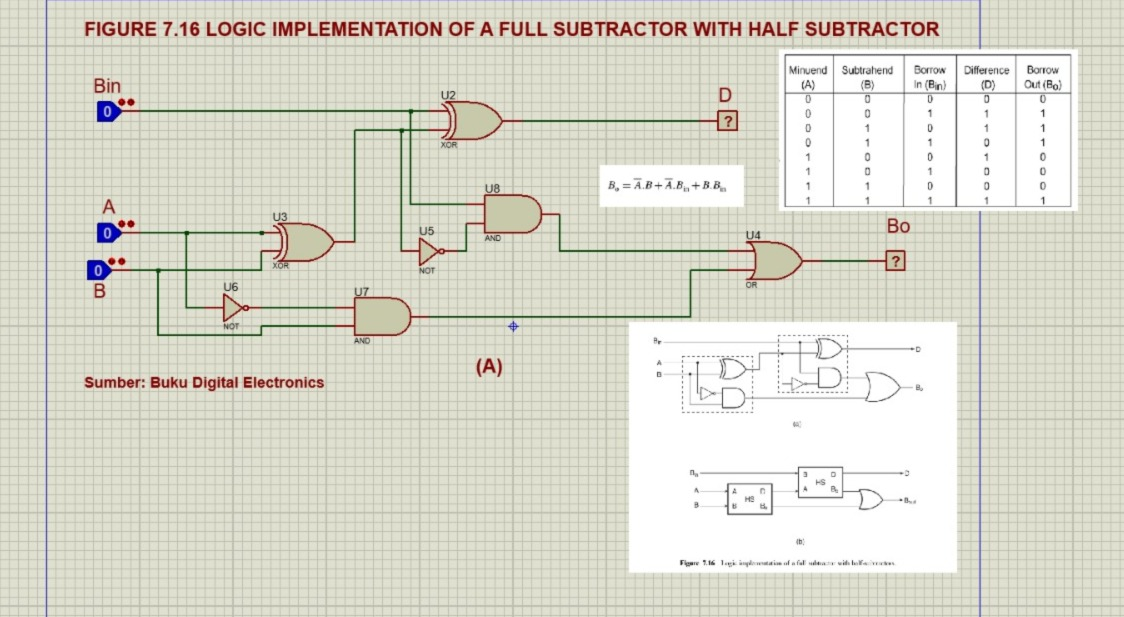

half substractor pertama melakukan operasi XOR pada bit masukan A dan B, dan operasi AND pada A' dan B untuk menghasilkan bit pinjaman antara.

half substractor kedua melakukan operasi XOR pada keluaran gerbang XOR pertama dan bit pinjaman masukan (bin), dan gerbang AND pada rangkaian setengah kedua menghasilkan keluaran yang sama dengan (A'B + AB')'.bin.

Keluaran gerbang XOR kedua adalah bit berbeda keluaran (d), dan bit pinjaman keluaran (b) diperoleh dengan meng-OR-kan keluaran dua gerbang AND.

Dalam elektronika digital, substractor adalah rangkaian logika kombinasional yang melakukan pengurangan dua bilangan biner. Namun, pengurangan bilangan biner dapat dilakukan menggunakan rangkaian penjumlah dengan mengambil komplemen 1 atau 2. Namun, kita juga dapat mewujudkan rangkaian khusus untuk melakukan pengurangan dua bilangan biner.

Dalam pengurangan dua bilangan biner, setiap bit pengurang dari bilangan tersebut dikurangi dari bit minuend signifikan yang bersesuaian untuk membentuk bit selisih. Selama pengurangan, jika bit minuend lebih kecil dari bit pengurang, maka 1 dipinjam dari posisi berikutnya. Tergantung pada jumlah bit yang diambil sebagai input, terdapat dua jenis pengurang, yaitu, Pengurang Setengah dan Pengurang Penuh.

half substractor adalah pengurang yang mengambil dua digit biner sebagai input dan menghasilkan bit selisih dan bit pinjaman (jika ada) sebagai output.

Di sisi lain, full substractor adalah pengurang yang menerima tiga bit sebagai masukan, yaitu dua bit masukan dan satu bit pinjaman masukan dari tahap sebelumnya, dan menghasilkan satu bit selisih dan satu bit pinjaman keluaran sebagai keluaran.

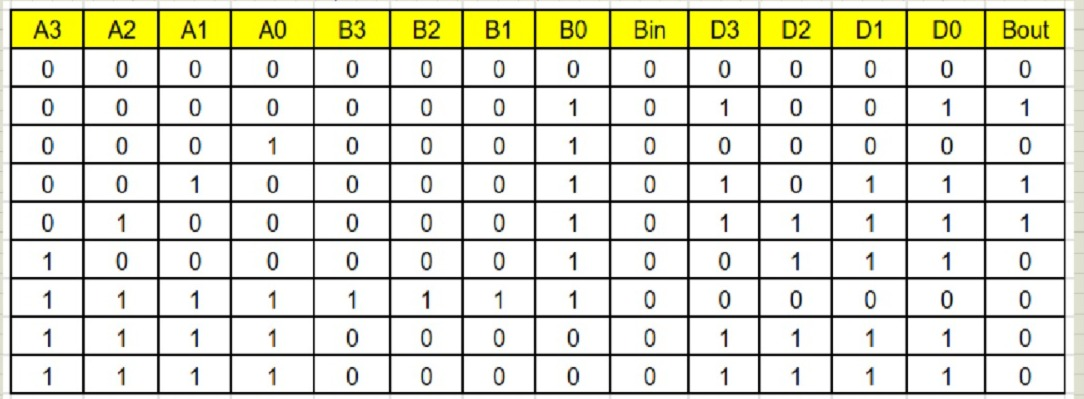

3) 7.17 Four-Bit Subtractor.

Pengurang biner 4-bit terdiri dari empat penjumlah penuh 1-bit yang dihubungkan secara seri. Hal ini memungkinkan pengurang untuk menangani empat bit informasi sekaligus. Penjumlah penuh adalah rangkaian kombinasional yang menjumlahkan dua bilangan biner dan menghasilkan keluaran penjumlahan dan keluaran simpan. Penjumlah penuh menerima tiga masukan, yaitu dua bilangan biner yang akan dijumlahkan dan satu bit simpan dari tahap sebelumnya. Keluaran penjumlahan dari setiap tahap dikirim ke tahap berikutnya dan keluaran simpan ditambahkan ke bit orde lebih tinggi berikutnya dari bilangan biner tersebut.

Pengurang biner 4-bit digunakan untuk melakukan pengurangan antara dua bilangan biner 4-bit. Masukan ke pengurang adalah dua bilangan biner 4-bit, yaitu bilangan yang dikurangi dan bilangan yang dikurangi. Pengurang akan menghasilkan selisih antara kedua masukan tersebut sebagai bilangan biner 4-bit.

Pengurang biner 4-bit dapat diimplementasikan menggunakan diagram rangkaian logika. Diagram ini menunjukkan masukan dan keluaran pengurang dan bagaimana keduanya terhubung ke gerbang logika. Gerbang logika yang digunakan dalam pengurang adalah gerbang AND, OR, XOR, dan NOT. Rangkaian logika dirancang menggunakan persamaan aljabar Boolean untuk gerbang logika.

Pengurang biner 4-bit digunakan dalam berbagai aplikasi seperti unit logika aritmatika (ALU), prosesor komputer, dan rangkaian logika. Pengurang juga digunakan dalam aplikasi ilmiah seperti pemrosesan sinyal digital. Pengurang merupakan komponen penting dalam rangkaian logika digital dan digunakan di berbagai jenis komputer dan perangkat elektronik.

Pengurang biner 4-bit adalah alat yang ampuh untuk melakukan operasi pengurangan biner. Dengan diagram rangkaian logikanya yang sederhana, alat ini dapat dengan mudah dipahami dan diimplementasikan dalam berbagai aplikasi. Pengurang biner 4-bit merupakan komponen penting dalam rangkaian logika digital dan digunakan dalam berbagai aplikasi.

Rangkaian full subtractor memiliki tiga buah input yaitu A (minuend), B (subtrahend), dan Bin (borrow in), serta dua output yaitu D (Difference) dan Bo (Borrow out). Untuk memahami kerja full subtractor secara menyeluruh, kita perlu menganalisis seluruh kombinasi input biner 3-bit (sebanyak 8 kombinasi). Perhitungan dilakukan berdasarkan rumus:

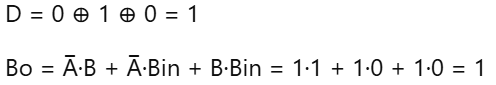

Berdasarkan tabel tersebut, kita dapat melihat bagaimana output D dan Bo berubah sesuai dengan perubahan kombinasi input. Misalnya, saat A=0, B=1, dan Bin=0, maka:

Jadi hasilnya:

- D3 D2 D1 D0 = 0000

- BOUT = 1

Artinya, 1011 - 0101 = 0000 dengan pinjaman akhir, menandakan hasil negatif dalam representasi 2’s complement.

2) Dalam implementasi logika full subtractor menggunakan dua half subtractor dan satu gerbang OR, berapakah output-nya jika A = 0, B = 1, dan Bin = 1?

Langkah 1 – Half Subtractor pertama (A - B):

D₁ = A ⊕ B = 0 ⊕ 1 = 1

Bo₁ = A̅ · B = 1 · 1 = 1

Langkah 2 – Half Subtractor kedua (D₁ - Bin):

D = D₁ ⊕ Bin = 1 ⊕ 1 = 0

Bo₂ = D₁̅ · Bin = 0 · 1 = 0

Langkah 3 – Gabungkan borrow:

Bo = Bo₁ + Bo₂ = 1 + 0 = 1

Jadi output akhirnya:

Borrow Out (Bo) = 1

Ini berarti hasil 0 - 1 - 1 adalah negatif (terjadi peminjaman).

6. Soal Pilihan Ganda[Kembali]

1) Figure 7.14 Full Substractor

Full subtractor adalah rangkaian logika kombinasional yang digunakan untuk melakukan pengurangan tiga bit masukan, yaitu A, B, dan Bin (borrow in). Rangkaian ini menghasilkan dua keluaran, yaitu Difference (D) dan Borrow out (Bo). Operasi pengurangan dilakukan secara logis dengan mengimplementasikan beberapa gerbang logika seperti XOR, AND, OR, dan NOT. Output Difference dihasilkan dari operasi XOR tiga input, yaitu A ⊕ B ⊕ Bin. Rangkaian ini menggunakan dua gerbang XOR secara bertahap, di mana input A dan B terlebih dahulu dioperasikan dengan XOR, lalu hasilnya di-XOR-kan lagi dengan Bin untuk menghasilkan D. Sementara itu, output Borrow out (Bo) dihasilkan melalui dua kondisi: pertama, ketika A lebih kecil dari B, dan kedua, ketika hasil XOR dari A dan B lebih kecil dari Bin. Untuk menghasilkan Bo, digunakan kombinasi gerbang NOT, AND, dan OR. NOT digunakan untuk membalik logika A dan hasil XOR dari A dan B, lalu hasil ini dioperasikan menggunakan AND bersama input lainnya, dan akhirnya disatukan menggunakan OR untuk menghasilkan Bo. Dengan kata lain, Bo akan bernilai 1 jika dibutuhkan pinjaman dari digit lebih signifikan. Rangkaian ini memungkinkan proses pengurangan bit digital dengan akurasi tinggi dan dapat digunakan dalam sistem digital lebih kompleks seperti ALU (Arithmetic Logic Unit) dan sistem komputer lainnya.

2) Figure7.16 Logic Implementation of a full substractor with half substractor

Rangkaian pada gambar ini merupakan implementasi logika dari full subtractor yang dibangun menggunakan dua buah half subtractor dan satu gerbang OR. Full subtractor berfungsi untuk melakukan operasi pengurangan tiga bit yaitu A - B - Bin (borrow in). Dalam desain ini, rangkaian bekerja dengan prinsip modularisasi, memanfaatkan dua blok half subtractor yang disusun secara berurutan.

Pertama, masukan A dan B dimasukkan ke half subtractor pertama (HS1) yang terdiri dari gerbang XOR (U3) untuk menghasilkan selisih awal (difference sementara) dan gerbang NOT (U6) serta AND (U7) untuk menghasilkan pinjaman awal. Output selisih dari HS1 kemudian digunakan sebagai salah satu input ke half subtractor kedua (HS2) bersama dengan input Bin, dan diproses melalui gerbang XOR (U2) untuk menghasilkan output akhir D (Difference).

Sementara itu, untuk menghasilkan Bo (Borrow out), digunakan dua jalur logika. Jalur pertama berasal dari borrow dari HS1 (hasil AND antara NOT A dan B). Jalur kedua adalah kombinasi logika dari NOT hasil XOR A⊕B dengan Bin (melalui U5 dan U8), yang menghasilkan borrow kedua dari HS2. Kedua sinyal borrow ini digabung menggunakan gerbang OR (U4), sehingga menghasilkan Bo akhir. Persamaan logikanya sesuai dengan yang tertulis pada gambar:

Rangkaian pada gambar ini merupakan implementasi logika dari full subtractor dengan menggunakan dua buah half subtractor yang disusun secara bertingkat dan satu gerbang OR sebagai penggabung sinyal borrow. Full subtractor sendiri berfungsi untuk menghitung pengurangan tiga bit masukan, yaitu A (minuend), B (subtrahend), dan Bin (borrow in), serta menghasilkan dua keluaran, yaitu D (difference) dan Bo (borrow out). Proses kerja rangkaian ini dimulai dari half subtractor pertama (SUB1), yang menerima input A dan B, kemudian menghasilkan selisih sementara dan sinyal borrow pertama. Selisih sementara ini kemudian menjadi input ke half subtractor kedua (SUB2) bersama dengan input Bin. SUB2 kemudian menghasilkan output akhir difference D dan sinyal borrow kedua. Kedua sinyal borrow dari SUB1 dan SUB2 kemudian digabung melalui gerbang OR untuk menghasilkan sinyal borrow akhir Bo. Dengan demikian, sinyal Bo akan bernilai 1 jika salah satu dari kondisi berikut terjadi: A lebih kecil dari B, selisih A - B lebih kecil dari Bin, atau nilai B dan Bin keduanya adalah 1. Implementasi ini secara sederhana menggambarkan bagaimana full subtractor dapat direalisasikan menggunakan dua modul half subtractor yang saling terhubung, membuat desain rangkaian lebih modular dan mudah dipahami baik secara teori maupun secara praktik menggunakan IC atau blok logika digital.

3) Figure 7.17 Four-Bit Subtractor.

Rangkaian ini merupakan implementasi dari pencacah pengurang 4-bit (Four-Bit Subtractor) yang terdiri dari empat blok full subtractor (SUB1 hingga SUB4), disusun secara berantai untuk menghitung pengurangan antara dua bilangan biner 4-bit, yaitu A3A2A1A0 dikurangi dengan B3B2B1B0. Proses pengurangan dilakukan secara bertahap mulai dari bit paling rendah (LSB) hingga bit paling tinggi (MSB), mengikuti prinsip borrow berantai antar full subtractor. SUB1 menerima input A0 dan B0 serta sinyal pengurang awal (Bin/SIN), kemudian menghasilkan output difference D1 dan sinyal borrow ke SUB2. Output borrow ini diteruskan ke SUB2 bersama dengan input A1 dan B1, dan proses berlanjut secara berantai hingga SUB4 yang menerima input A3 dan B3 beserta borrow dari SUB3. Setiap full subtractor menghasilkan satu bit selisih (D1–D4), dan sinyal borrow terakhir dari SUB4 ditampilkan sebagai BOUT yang menunjukkan apakah hasil pengurangan memerlukan peminjaman tambahan dari bit lebih tinggi.

Dengan konfigurasi ini, rangkaian memungkinkan pengurangan dua bilangan biner 4-bit dengan efisiensi dan akurasi tinggi, serta menunjukkan konsep pengurangan biner secara sistematis menggunakan logika kombinasi. Hasil selisih akhir akan ditampilkan pada empat output D (D4–D1), sementara kondisi pinjaman antar-bit ditelusuri melalui jalur sinyal borrow antar full subtractor. Rangkaian ini umum digunakan dalam unit aritmatika digital seperti ALU (Arithmetic Logic Unit) dan sistem pemrosesan data digital lainnya.

Komentar

Posting Komentar