Chapter 8

- Mampu Membuat Rangkaian Multiplexer for parallel-to-serial conversion, Logic Function Implementation Circuit Using 4-to-1 Multiplexer (MUX) dan Multiplexer 8-to-1 with IC 74151

- Memahami Fungsi Komponen pada rangkaian Multiplexer for parallel-to-serial conversion, Logic Function Implementation Circuit Using 4-to-1 Multiplexer (MUX) dan Multiplexer 8-to-1 with IC 74151.

- Mengetahui Prinsip Kerja dari Rangkaian Multiplexer for parallel-to-serial conversion, Logic Function Implementation Circuit Using 4-to-1 Multiplexer (MUX) dan Multiplexer 8-to-1 with IC 74151

- IC 74151

- IC 4 to 1 MUX

- Gerbang NOT

- Logic State

1) Figure 8.11 Multiplexer for parallel-to-serial conversion.

Konversi paralel ke serial adalah proses pengubahan data dari bentuk paralel, di mana semua bit dikirim secara bersamaan, menjadi bentuk serial, di mana bit dikirim satu per satu secara berurutan. Teknik ini sangat umum digunakan dalam sistem komunikasi digital dan antarmuka data, terutama untuk menghemat jumlah jalur transmisi.

Salah satu cara paling efisien untuk melakukan konversi ini adalah dengan menggunakan multiplexer (MUX). Multiplexer merupakan rangkaian logika kombinasi yang berfungsi untuk memilih salah satu dari beberapa input data dan meneruskannya ke satu output tunggal berdasarkan kombinasi dari sinyal selektor (selector input). Pada konversi paralel ke serial, MUX digunakan untuk membaca satu per satu data input paralel sesuai urutan, dan mengeluarkannya secara berurutan sebagai output serial.

Misalnya, pada multiplexer 8-to-1, terdapat 8 input data (X0 hingga X7) dan 3 input selektor (S2, S1, S0). Ketika sinyal selektor diberikan kombinasi biner tertentu, hanya satu input yang akan diteruskan ke output. Untuk mendapatkan aliran data serial, selektor diatur secara otomatis berurutan (menggunakan rangkaian pencacah atau counter) sehingga multiplexer memilih input dari X0 ke X7 satu per satu sesuai urutan bit. Dengan setiap pulsa clock, multiplexer akan berpindah memilih input berikutnya dan mengirimkan bit tersebut ke output serial.

Rangkaian ini sangat penting dalam sistem komunikasi data, seperti UART, sistem transmisi data mikroprosesor, dan alat perekaman digital, di mana efisiensi pengiriman data sangat bergantung pada bentuk serial. Selain itu, penggunaan multiplexer juga menyederhanakan desain rangkaian tanpa memerlukan register shift tambahan.

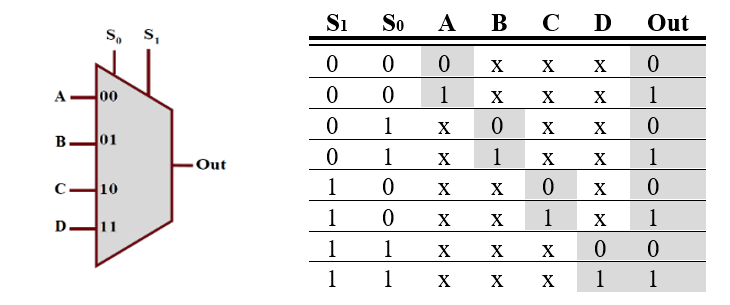

2) Figure 8.12: Example 8.1 Logic Function Implementation Circuit Using 4-to-1 Multiplexer (MUX)

Multiplexer (MUX) adalah rangkaian logika kombinasi yang digunakan untuk memilih satu dari beberapa input dan meneruskannya ke output tunggal, berdasarkan kombinasi input selektor. Selain digunakan untuk pemilihan data, multiplexer juga dapat dimanfaatkan untuk mengimplementasikan fungsi logika, terutama fungsi logika kombinasi yang bergantung pada beberapa variabel input.

Dalam kasus multiplexer 4-to-1, terdapat 4 input data (I0 hingga I3), 2 input selektor (biasanya disebut S1 dan S0), dan satu output. Input selektor ini berfungsi untuk memilih salah satu dari input data berdasarkan nilai biner selektor. Untuk mengimplementasikan fungsi logika 3 variabel (misalnya A, B, dan C), dua dari variabel tersebut digunakan sebagai input selektor, sementara satu variabel lainnya digunakan untuk menentukan nilai input data pada masing-masing I0 sampai I3.

Cara kerjanya adalah dengan membentuk tabel kebenaran dari fungsi logika yang akan diimplementasikan, lalu menganalisis kombinasi nilai selektor (misalnya A dan B) untuk setiap baris. Berdasarkan nilai variabel ketiga (misalnya C), input I0–I3 diisi dengan nilai logika tetap (0 atau 1), atau dengan variabel C atau komplemennya (C̅). Dengan demikian, ketika input selektor aktif pada kombinasi tertentu, multiplexer akan memilih input data yang telah disusun sesuai kebutuhan fungsi, dan output akan mengikuti nilai fungsi logika tersebut.

Metode ini sangat efisien karena hanya memerlukan satu chip MUX untuk mewakili suatu fungsi logika yang bisa jadi memerlukan banyak gerbang logika jika dibuat secara konvensional. Penggunaan multiplexer untuk implementasi fungsi logika juga mempermudah desain sistem digital terintegrasi seperti dalam rangkaian pengendali, decoder, dan ALU (Arithmetic Logic Unit).

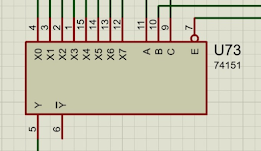

3) Figure 8.13 Example 8.2 Multiplexer 8-to-1 with IC 74151

Multiplexer (MUX) adalah komponen logika kombinasi yang berfungsi untuk memilih satu dari beberapa input dan meneruskannya ke satu output berdasarkan kombinasi dari sinyal selektor. IC 74151 adalah salah satu jenis multiplexer 8-to-1, yang berarti memiliki 8 input data (D0 hingga D7), 3 input selektor (S2, S1, S0), serta dua output, yaitu output asli (Y) dan output komplemen (W = Y̅).

Cara kerja IC 74151 adalah dengan membaca nilai dari tiga input selektor (S2, S1, dan S0), yang menentukan salah satu dari delapan input data untuk diteruskan ke output Y. Kombinasi nilai selektor diinterpretasikan sebagai bilangan biner 3-bit, yang dikonversi ke angka desimal dari 0 sampai 7. Misalnya, jika S2 = 1, S1 = 0, dan S0 = 1, maka kombinasi biner tersebut adalah 101, yang setara dengan desimal 5. Dengan demikian, input D5 akan dipilih dan diteruskan ke output Y.

IC 74151 juga memiliki pin strobe (G̅) sebagai input aktif rendah. Ketika pin strobe berada pada logika tinggi (1), output akan disable (tidak aktif), sedangkan saat G̅ = 0, IC bekerja normal. IC ini juga menyediakan output komplemen, sehingga sangat berguna dalam implementasi fungsi logika yang memerlukan pembalikan output secara langsung.

Multiplexer 8-to-1 seperti 74151 sangat berguna dalam aplikasi digital, termasuk pengolahan data, implementasi fungsi logika kombinasi, pemilihan jalur data (data selector), serta dalam pembuatan kontrol mikroprosesor dan sistem komunikasi. Dengan menyusun input data secara logis (misalnya berdasarkan fungsi dari variabel A, B, C, dan D), IC 74151 dapat digunakan untuk membentuk fungsi logika kompleks secara praktis tanpa memerlukan banyak gerbang logika

MUX akan memilih input berdasarkan selektor dari 000 sampai 111 (0 sampai 7). Jadi:

2) Jika clock berhenti di siklus ke-5:

Output terakhir adalah pada selektor = 100 → X4 = 1

Jawaban: 1

6. Soal Pilihan Ganda[Kembali]

A. 1, 1, 0, 1, 0, 0, 1, 0

B. 0, 1, 0, 0, 1, 0, 1, 1

C. 0, 1, 0, 0, 1, 0, 1, 0

D. 1, 0, 0, 1, 0, 0, 1, 1

A. 0

B. 1

C. C

D. C̅

3) Dalam sebuah rangkaian IC 74151, jika A = 1, B = 0, C = 1, maka input ke berapa yang akan dipilih oleh MUX?

A. I5

B. I4

C. I3

D. I6

1) Figure 8.11 Multiplexer for parallel-to-serial conversion.

Rangkaian ini merupakan implementasi dari konversi data paralel ke serial menggunakan multiplexer 8-to-1 (74151). Tujuan utama dari rangkaian ini adalah untuk mengubah data 8-bit paralel menjadi aliran data 1-bit secara serial yang dapat dikirimkan atau diproses satu per satu dalam sistem digital.

Pada bagian input, terdapat 8 buah data input paralel (dari MSB ke LSB) yang masing-masing dihubungkan ke pin X0 hingga X7 dari IC multiplexer 74151 (U1). Multiplexer ini memiliki tiga pin seleksi yaitu S2, S1, dan S0 (pin A, B, dan C) yang menentukan input mana yang akan dilewatkan ke output (Y) secara berurutan.

Tiga buah flip-flop tipe toggle (pembagi frekuensi/clock divider) digunakan untuk mengontrol pemilihan input multiplexer secara berurutan. Flip-flop ini menghasilkan sinyal S0, S1, dan S2 yang akan menghitung dari 000 hingga 111 secara biner. Setiap kombinasi dari S2S1S0 akan memilih salah satu dari delapan input paralel pada multiplexer.

Ketika clock diberikan pada input clock (bagian bawah kanan), maka sinyal dari flip-flop akan naik secara berurutan dan memilih satu per satu input paralel dari X0 ke X7. Output multiplexer Y = Xn, sesuai dengan kombinasi biner dari S2S1S0. Output ini menjadi output serial, yaitu data yang sebelumnya paralel sekarang dikirimkan satu per satu berdasarkan urutan bitnya.

Contohnya, jika data paralel awal adalah 10101101, maka setiap pulsa clock akan menghasilkan output serial: 1, 0, 1, 0, 1, 1, 0, 1 secara berurutan di pin Y.

Rangkaian ini umum digunakan dalam sistem komunikasi digital, konversi data, dan antarmuka mikroprosesor untuk mengurangi jumlah jalur data fisik.

2) Figure 8.12: Example 8.1 Logic Function Implementation Circuit Using 4-to-1 Multiplexer (MUX)

Rangkaian ini menunjukkan cara mengimplementasikan suatu fungsi logika menggunakan multiplexer 4-ke-1 (4-to-1 MUX). Fungsi logika tersebut bergantung pada tiga variabel input: A, B, dan C, di mana A dan B digunakan sebagai selector (S0 dan S1), sedangkan C digunakan sebagai input data yang dikendalikan oleh kondisi logika dari fungsi target.

Multiplexer 4-to-1 memiliki 4 input data (I0 sampai I3), 2 input selektor (S1 dan S0), dan 1 output (F). Kombinasi nilai dari B dan A akan menentukan input mana (dari I0–I3) yang akan diteruskan ke output F. Input-input ini diisi berdasarkan fungsi logika f(A,B,C) yang didefinisikan dalam tabel kebenaran (Truth Table – Tabel 8.5).

Langkah-langkahnya sebagai berikut:

Selector S1 dan S0 diisi dari input B dan A.

Karena B = 1 dan A = 0 (sesuai gambar), maka nilain = (B·2) + A = (1·2) + 0 = 2, artinya input I2 akan dipilih.Berdasarkan tabel implementasi (Table 8.6), nilai dari I2 adalah logika C, artinya output F akan mengikuti nilai dari input C.

Karena pada kondisi gambar, C = 1, maka output F = 1.

Dengan kata lain, multiplexer bertindak sebagai pemilih berdasarkan kombinasi dua bit selector (B dan A), dan meneruskan input data logika (berupa 0, 1, C, atau NOT C) sesuai isi fungsi. Ini merupakan metode efisien untuk mengimplementasikan fungsi logika kombinasi hanya dengan menggunakan komponen multiplexer, tanpa memerlukan gerbang logika tambahan.

3) Figure 8.13 Example 8.2 Multiplexer 8-to-1 with IC 74151

Rangkaian pada gambar merupakan implementasi fungsi logika menggunakan multiplexer 8-ke-1 (8-to-1) dengan IC 74151. Multiplexer ini memiliki delapan input data (I0 hingga I7), tiga input selektor (S2, S1, dan S0), serta satu output utama (Y). Dalam rangkaian ini, tiga buah variabel logika yaitu A, B, dan C berfungsi sebagai selektor input, di mana A dihubungkan ke S2, B ke S1, dan C ke S0. Kombinasi ketiga input selektor ini akan membentuk bilangan biner 3-bit yang dikonversi ke bilangan desimal (n = S2·4 + S1·2 + S0), yang menentukan input mana dari I0 sampai I7 yang akan dihubungkan ke output Y.

Pada kondisi yang ditunjukkan di gambar, nilai A = 1, B = 1, dan C = 1, maka nilai n adalah 7. Artinya, input I7 akan dipilih oleh MUX dan diteruskan ke output Y. Nilai dari setiap input I0 sampai I7 ditentukan berdasarkan fungsi logika yang ingin diimplementasikan, sebagaimana terlihat pada Tabel 8.7 di bawah rangkaian. Selain itu, terdapat gerbang NOT (U74) yang digunakan untuk menghasilkan nilai komplemen dari variabel D (yaitu D̅) sehingga input ke MUX bisa berupa D maupun D̅ sesuai kebutuhan fungsi. Dalam kasus ini, output Y akan mengikuti nilai dari I7, yang dapat berupa 0, 1, D, atau D̅, tergantung bagaimana fungsi disusun.

Secara keseluruhan, rangkaian ini menunjukkan bagaimana sebuah multiplexer 8-ke-1 dapat digunakan untuk menggantikan rangkaian logika kombinasi yang lebih kompleks, cukup dengan memanfaatkan input selektor dan mengatur nilai tetap atau variabel pada input datanya. Pendekatan ini sangat efisien untuk implementasi logika dalam skala besar pada sistem digital.

Komentar

Posting Komentar